현재 글은 컴퓨터 구조와 아키텍처 서적 및 대학에서 들은 강의를 기반으로 한다.

Instruction Set 디자인에서 고려할 사항

- Operation repertoire: 얼마나 많은 operation이 있나? 구성 및 복잡한 정도는 어떤가?

- Data Types

- Instruction formats: opcode 필드 길이, 주소의 개수( instruction에서 사용하는 주소: 3, 2, 1, 0 address )

- Register

- Addressing modes

- CISC vs RISC

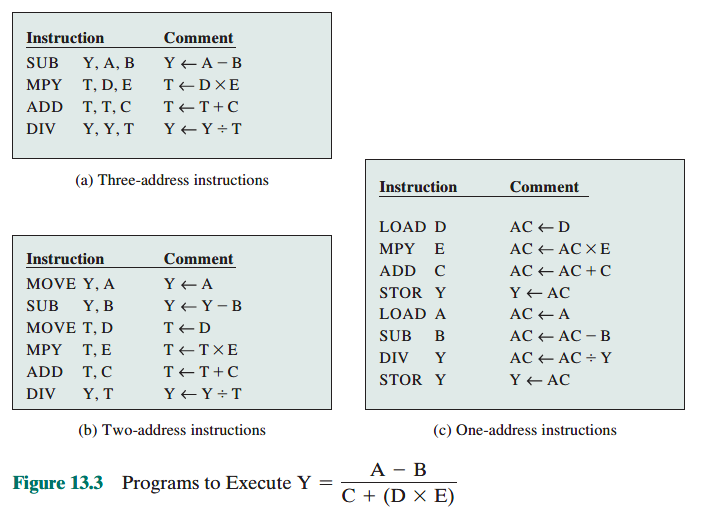

Number of address

각각의 instuction에 몇 개의 address가 존재하는지를 결정할 수 있다. 현실에서 사용하는 대부분의 연산은 unary 또는 binary로 표현되므로 최소 2개의 operand을 위한 주소가 필요하다. 이때 해당 주소를 저장하는 공간까지 연산에서 다루는 경우 3개의 주소를 사용할 수 있다.

이러한 방식으로 instruction에 사용되는 address의 종류는 총 4가지가 존재한다.

- zero-address instruction: 스택 기반 push / pop을 통해 주소 없이 연산을 수행할 수 있다.

- one-address instruction: 2개의 operand 중 하나가 AC 레지스터라 주소가 하나만 있으면 된다.

- two-address instruction: 2개의 operand을 위한 주소를 가진다.

- three-address instruction: 2개의 operand 및 연산 결과를 반환할 위치에 대한 주소를 가진다.

| 주소의 개수 | 기호 표현 | 코드 |

| 3 | OP A,B,C | A <- B OP C |

| 2 | OP A,B | A <- A OP B |

| 1 | OP A | AC <- AC OP A |

| 0 | OP | T <- (T-1) OP T |

AC: accumulator

T : 스택의 top

A,B,C 레지스터또는 메모리

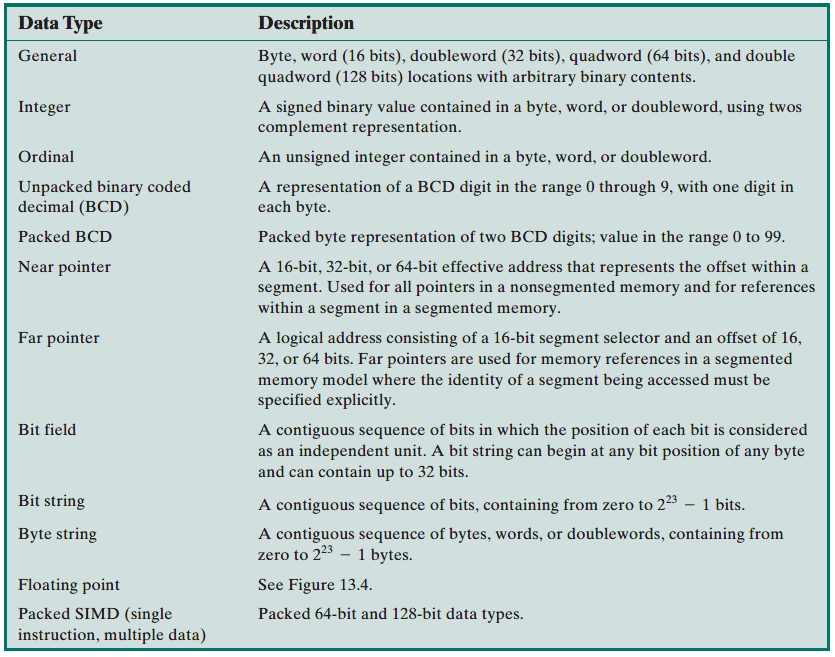

데이터 타입

X86의 데이터 타입

데이터 길이에 따른 구분

- byte(8)

- word(16)

- double word(32)

- quad-word(64)

- double quad-word(128)

데이터 타입들

- BCD: 4비트를 이용하여 0~9 사이의 숫자를 표현하는 방식. 91은 00001001 00000001로 표현 가능하다.

- Packed BCD

: 데이터 최소 전송 단위가 8비트(byte) 이므로 4비트만 필요하더라도 8비트 단위로 전송하여 4비트가 낭비되는 문제 발생. 이때 해당 4비트에도 숫자 하나를 할당하여 byte로 2개 숫자를 표현할 수 있음. 91 = 10010001 - Near Pointer: 세그먼트 내의 주소를 표현.

- Far Pointer: 세그먼트 내의 공간은 최대 64비트의 크기만 표현 가능. 더 넓은 공간을 사용하고 싶은 경우 여러 세그먼트를 선택하는 16비트를 추가한 Far Pointer 사용.

ARM의 데이터 타입

데이터 길이에 따른 구분

- byte(8)

- halfword(16)

- word(32)

세가지 타입 모두 2의 보수 기반 정수 및 부호 없는 정수로 표현될 수 있다.

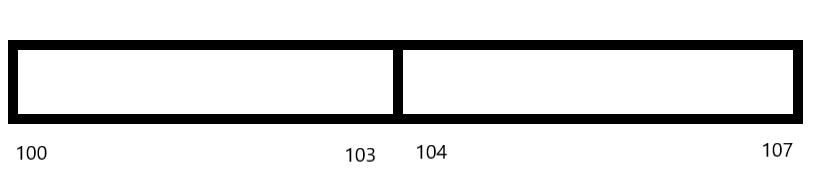

일반적으로 halfword 및 word는 자신의 타입에 맞게 aligned 되어 있어야 한다. 1 word로 데이터를 읽으면 32비트 단위로 전송된다. 따라서 word 데이터의 주소는 100, 104, 108 ... 과 같은 4의 배수로 할당될 수 있다. 이 상황에서 어떤 사람이 101번지부터 104번지까지의 데이터를 읽는다면 같은 32bit word 데이터를 읽더라도 100 ~ 107번지까지에 해당하는 모든 값을 읽어야 하는 오버헤드가 발생한다.

ARM은 이러한 오버헤드를 방지하기 위해 Alignment Checking을 통해 올바르지 않은 주소에 접근하는 경우 alignment fault을 발생시킨다. 100, 104, 108번지가 아닌 101번지를 접근하는 등 행위를 하면 fault가 발생하게 된다.

단, Unaligned Access에 대한 옵션이 켜져 있으면 앞에서 언급한 것처럼 여러 블럭을 읽어서 처리해준다고 한다.

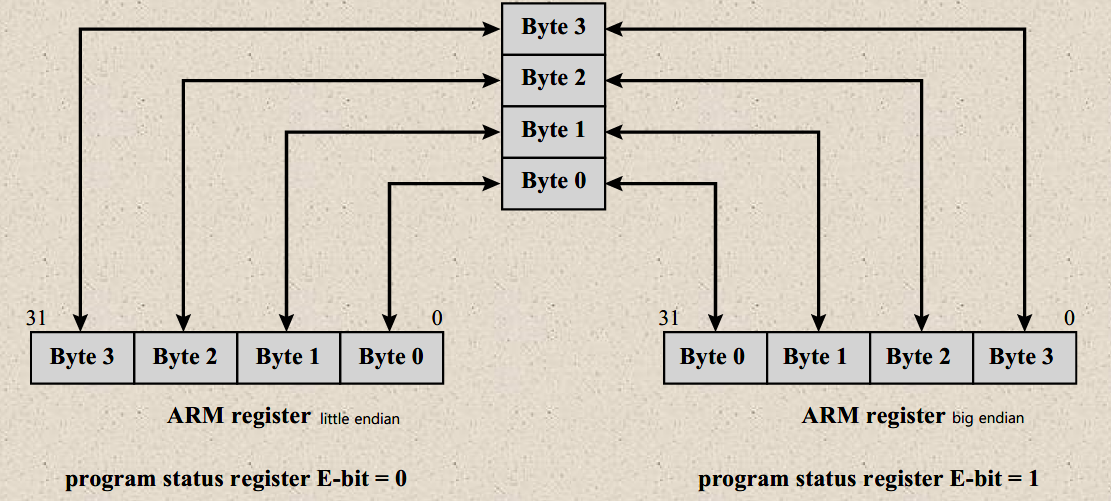

Byte Order

- Big Endian: 상위 바이트를 하위 주소에 먼저 저장하는 방식. 사람이 읽는 방식과 유사.

- Little Endian: 상위 바이트가 상위 주소에 저장하는 방식. 연산에 효율적이라고 함.

ARM은 기본적으로 Big Endian으로 설계되어 있지만 컴퓨터 시장을 사실상 장악하고 있는 x86 아키텍처가 Little Endian을 사용하기 때문에 상호 호환을 위해 E-bit라는 레지스터를 둬서 두 가지 방식을 선택할 수 있게 한다.

operation & processor action

- Data Transfer

- 데이터를 특정한 위치에서 다른 위치로 이동

- 메모리에 연관된 경우, 다음과 같은 요소들을 고려

- memory addressing mode

- virtual address을 real address로 변환

- memory read/write 개시

- Arithmetic, Logical, Conversion

- 연산 이전, 혹은 이후에 데이터 전송과 연관될 수 있음.

- ADD R1, 500의 경우 500번지 주소에 있는 값을 가져오는(tranfer) 작업이 필요.

- 특정한 머신의 경우 ALU와 Data Transfer이 동시에 수행될 수 있음.

- Condition code / flag setting을 통해 conditional branch 수행.

- 연산 이전, 혹은 이후에 데이터 전송과 연관될 수 있음.

- Transfer of control: Program Counter을 업데이트, conditional Branch 등 가능하게 함.

- I/O

- I/O 모듈 커맨드 실행.

- Memory-mapped I/O 경우 Memory-mapped address 결정

System Control

프로세서가 특권(privileged) 상태 또는 특별한 특권 메모리 영역에서 프로그램을 실행할 때만 실행되는 명령들이 있는데, 이러한 명령들은 일반 유저가 아닌 운영체제에 의해서 사용될 수 있도록 예약 되어 있다.

OS는 시스템을 관리하기 위해 다양한 값들을 읽고 변경할 수 있다. 캐시 / 메모리에 대한 write 정책 수립, 프로세스가 접근 가능한 주소 영역 지정(storage protection key), priority 설정 및 변경 등 다양한 측면에서 시스템의 값들이 관리된다. 이때 해당 값들은 컴퓨터 동작에 매우 중요한 역할을 하기 때문에 일반 사용자가 임의로 값을 변경할 수 없어야 한다. 이처럼 시스템 관리를 목적으로 운영체제만 사용할 수 있는 다양한 명령들을 system control instruction이라고 부른다.

- Control Register 값을 읽거나 변경할 수 있다.

- storage protection key을 읽거나 변경할 수 있다.

- 멀티프로그래밍 시스템에서 control block 접근.

Transfer of Control

- https://www.ibm.com/docs/en/cobol-zos/6.3?topic=structure-transfer-control

- https://www.computer-dictionary-online.org/definitions-t/transfer-of-control.html

다음 명령으로 순차적으로 이동하여 실행하는 대신, 특정 주소에서 프로그램을 계속하는 동작을 의미한다. 프로그램은 보통 정의된 순서에 따라 진행되지만, branch, skip, 프로시저 콜 등의 동작을 위해서는 PC에 특정한 주소 값을 지정, 해당 위치로 이동 해서 프로그램을 계속 진행해야 할 수 있다.

- instruction이 반복되어 사용되는 경우 코드 중복을 막기 위해 사용(모듈화)

- if branch 등 분기를 통해 프로그램이 decision making을 수행할 수 있도록

- 매커니즘을 작은 단위로 쪼개기 위해

Transfer of Control의 장점은 다음과 같다.

- Economy: 동일 코드를 재활용할 수 있다.

- Modularity: 코드를 모듈 단위로 쪼갤 수 있다.

Transfer of Control에서의 기본 instruction은 다음과 같다.

- Call: 현재 위치에서 다른 프로시저를 호출

- Return: 프로시저를 호출한 기존 위치로 돌아가기

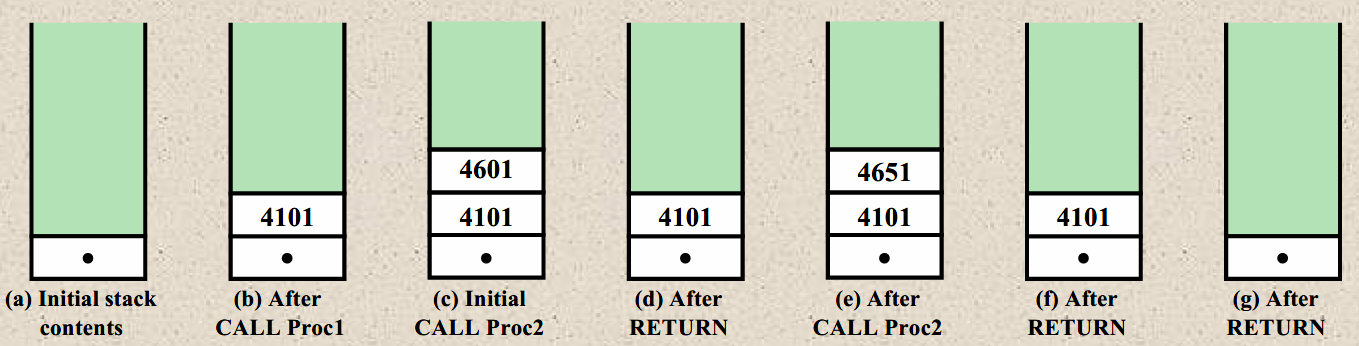

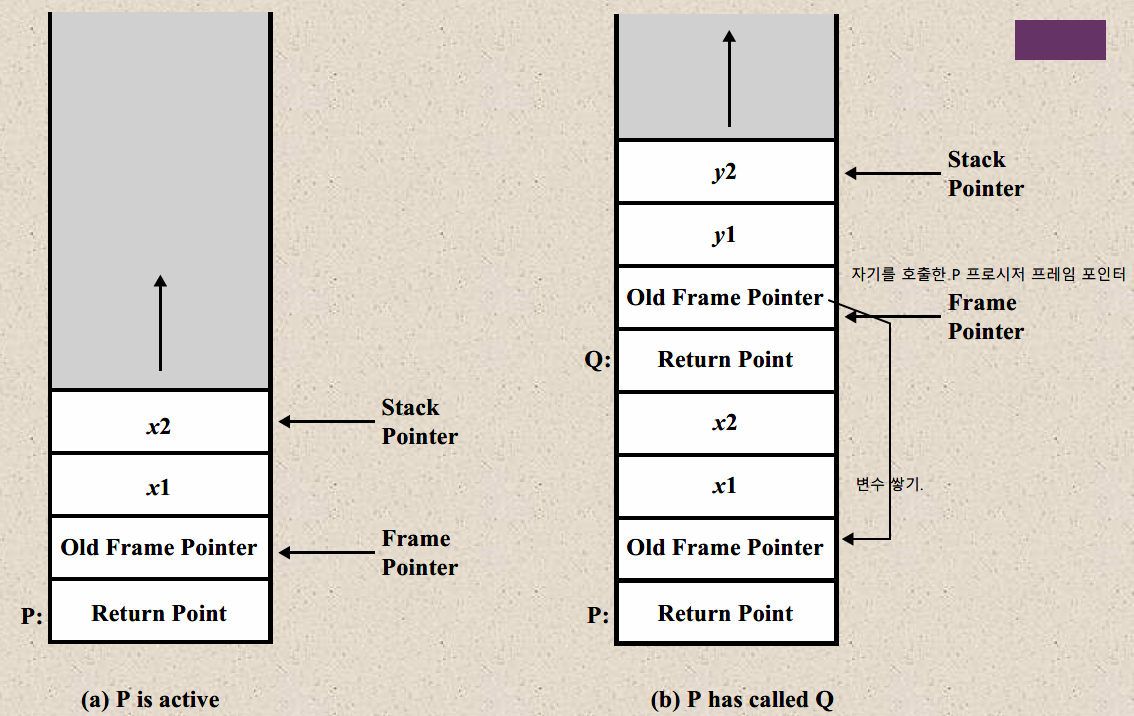

스택

- 스택 프레임: 매개변수, 지역변수 등 임시 변수를 저장하는 공간

- 스택 포인터 레지스터(ESP): 현재 스택이 가리키는 위치. 스택이 채워진 위치까지를 가리킨다.

- 프레임 포인터 레지스터(EBP): 현재 프레임의 시작 위치.

- 프레임 포인터: 되돌아갈 스택 프레임 위치를 저장한 포인터.

스택은 상위 주소에서 하위 주소로 채워진다.

새로운 프로시저가 호출될 때 동작

- 새로운 프로시저가 끝났을 때 돌아갈 주소(address)를 저장한다.

- 기존 프로시저가 사용하던 스택 프레임의 시작 위치(EBP)을 저장한다.

- 새로운 변수 등이 할당될 때 스택에 push.

x86 operations type

x86 아키텍처는 CISC 기반으로, 컴파일러 입장에서 더 최적화된 머신 언어 번역이 가능하도록 특별한 명령들을 포함한 매우 많은 동작을 제공한다. Call, Enter, Leave, Return이라는 명령을 가지며, Enter 및 Leave은 pascal 등 언어에 있는 nested procedure(함수 내부에 함수를 정의해서 사용하는 것)을 지원하기 위해 스택 포인터 및 프레임 포인터를 한번에 잡아주는 역할을 수행한다.

새로운 프로시저가 호출되면 다음과 같은 동작을 수행한다.

- 스택에 돌아갈 주소를 저장(push)한다.

- 스택에 현재 프레임 포인터를 저장한다.

- 스택 포인터를 프레임 포인터의 새 값으로 복사한다.

- 스택 포인터를 조정하여 프레임을 할당한다.

Status Bit

status bit은 특정 동작(값의 비교 등)에 의해 설정되는 비트 값으로, 해당 비트의 조합을 기준으로 상태 코드를 설정하여 conditional branch을 가능하게 한다. status bit가 존재하는 경우 비교 및 값에 따른 실행이 서로 다른 instruction이 되는데, 이 둘 사이에 dependency를 가지게 되므로 파이프라이닝이 어려워질 수 있다.

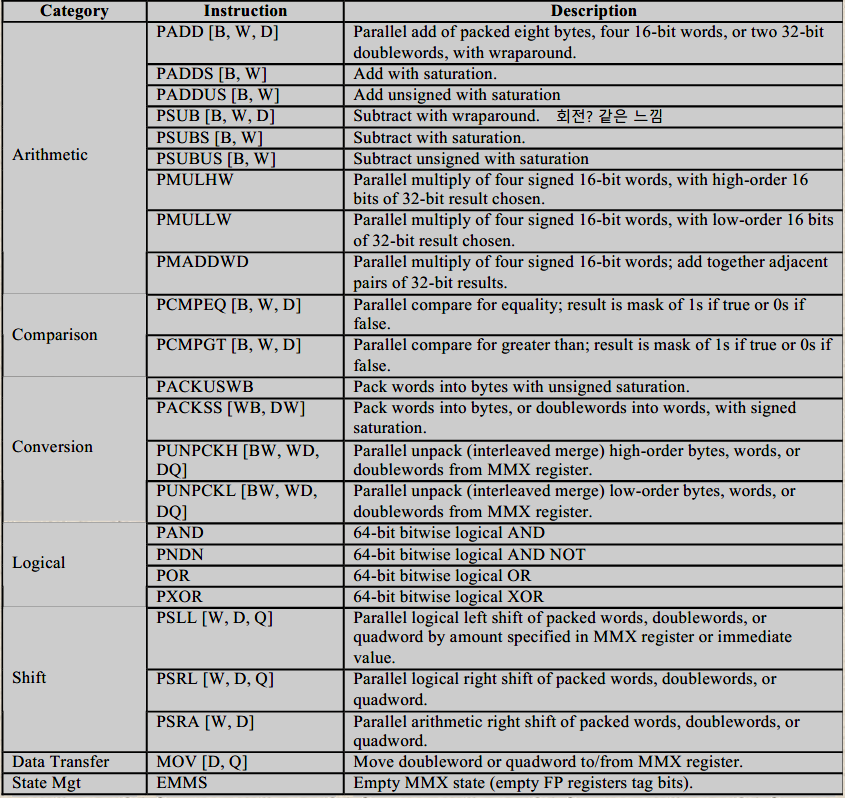

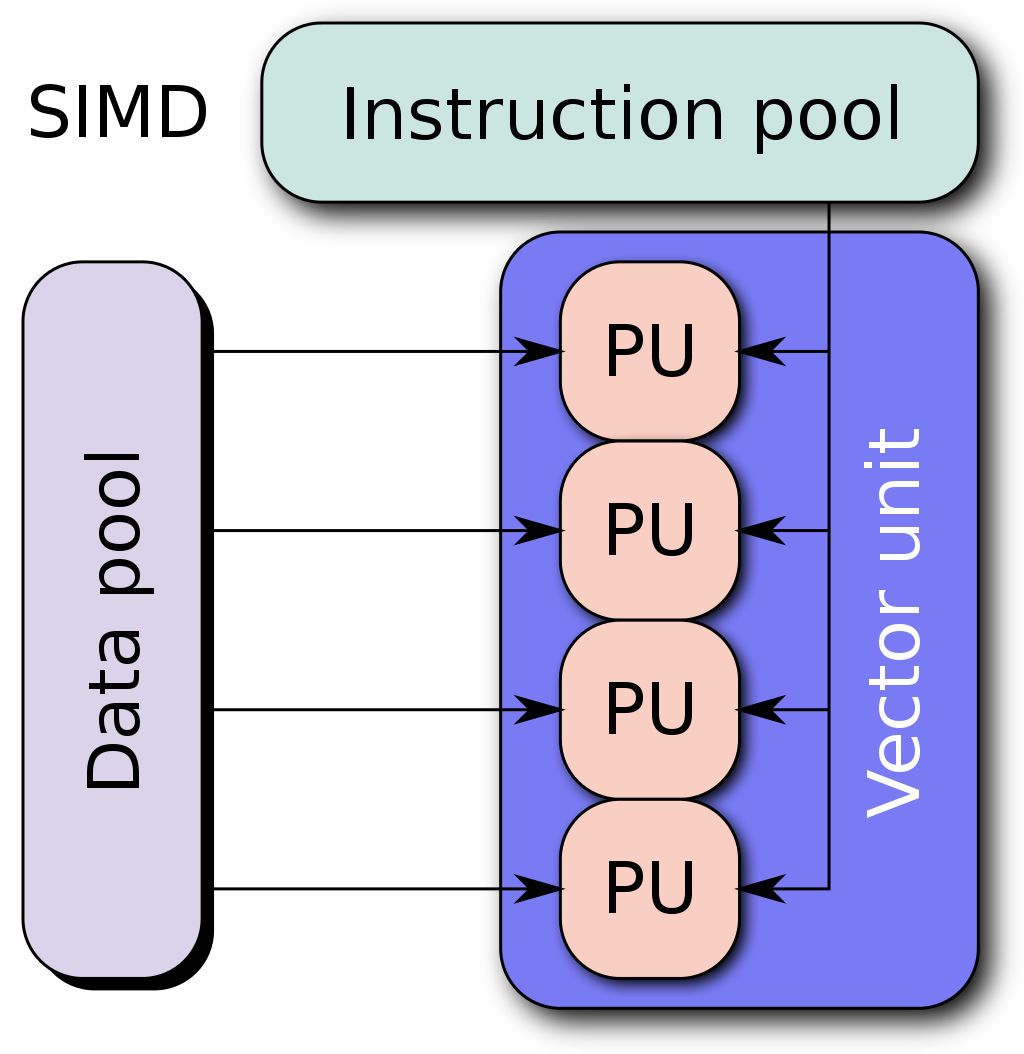

x86 SIMD(Single Instruction Multiple Data) Instructions

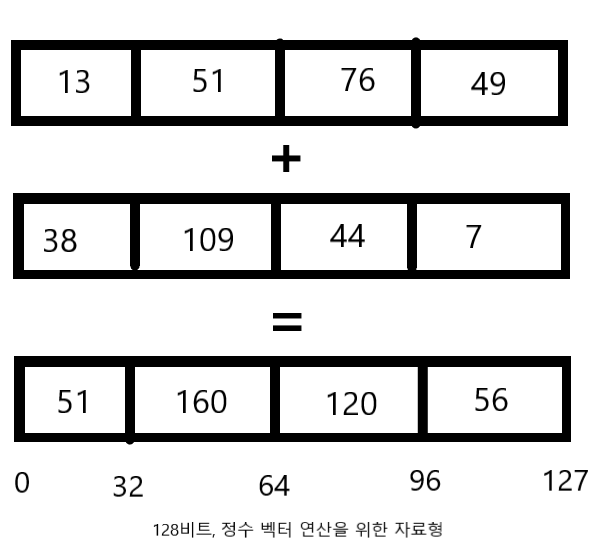

SIMD는 단일 연산을 다수의 데이터에 한번에 처리하는 방법을 의미한다. 비디오, 오디오 등 멀티미디어의 데이터는 작은 데이터 타입을 가지면서 개수가 매우 많다. 예를 들어 이미지를 구성하는 픽셀은 32비트 크기로 데이터 타입이 작은 편이지만, 400 * 400 크기의 섬네일 수준 이미지에도 16만개가 들어가는 등 규모가 엄청난 편이다. 멀티미디어 데이터에는 동일한 연산을 진행하는 경우가 많으므로, 하나의 연산을 여러개의 데이터에 동시에 처리할 수 있도록 하는 것이 SIMD이다.

SIMD 자료형 안에는 연산 대상이 되는 여러개의 동일 타입 데이터가 들어간다. 예를 들어 128비트의 SIMD 자료형 안에는 int형 데이터 4개가 동시에 들어갈 수 있다. 연산이 단일 명령만으로 수행된다는 점에서 높은 성능 향상을 가져올 수 있다.

그러나 SIMD 연산이 항상 가능한 것은 아니다. SIMD 연산의 대상이 되는 데이터는 서로 독립적 관계에 있어야 한다. 예를 들어 (A,B,C,D...) = (1,3,5,7...)와 Y = X + Y 라는 연산을 생각해보자.

| X | Y | X + Y |

| 1 | 3 | 4 |

| 4 | 5 | 9 |

| 9 | 7 | 16 |

| 16 | 9 | 25 |

| 25 | 11 | 36 |

연산 결과를 보면 Y = X + Y 은 이전 연산의 결과의 값에 종속적이다. 이처럼 연산에서 데이터 사이 종속 관계가 존재하는 경우 SIMD을 사용할 수 없다. 멀티 미디어에 SIMD 기법이 도입될 수 있는 이유는 데이터가 독립적이기 때문이다.

ARM Operation Type

- Load and Store

- Branch

- Data processing

- Multiply

- Parallel addition & Subtraction ( 멀티미디어 )

- Extend instruction ( byte -> halfword, word 확장 )

- status register access

RISC-V

RISC(reduced instruction set computer) 원칙을 기반으로 하는 공개 표준 ISA로, 오픈 소스 라이센스에 기반하여 누구든 무료로 사용할 수 있으며 다양한 전문가들이 자발적으로 개발 과정에 참여할 수 있다는 것이 특징이다.

- load-store 아키텍처

- CPU의 멀티플렉서를 단순화 하는 비트 패턴

- IEEE 754 부동소수점 실수

- 아키텍처 중립성: RISC-V ISA 이용해서 범용, 임베디드 등 다양한 종류의 칩을 만들 수 있음

- sign extension(부호 유지하면서 비트 수 늘리는 방법) 속도를 높이기 위해 MSB 위치 고정

- 명령어 셋은 다양한 방식의 사용을 위해 설계됨

- 가변길이 기반, 확장 가능해서 더 많은 인코딩 비트 추가 가능

- 임베디드, 개인 컴퓨터, 벡터 프로세서 기반 슈퍼컴퓨터, 병렬 컴퓨터 등 다양한 시스템 지원

- 더 넓은 메모리를 표현하기 위해 instruction set space을 128비트까지 확장

- 오픈 소스 기반 프로젝트이므로 버클리 대학의 구성원이 아니더라도 개발에 기여 가능

- privileged ISA(OS가 시스템 관리 위해 사용하도록 예약된 명령어들)가 고정되어 소프트웨어 및 하드웨어 개발 가능

'CS > 컴퓨터구조' 카테고리의 다른 글

| [컴퓨터구조] 프로세서 구조 및 기능(1) (0) | 2022.11.17 |

|---|---|

| [컴퓨터구조] Instruction set(2) (0) | 2022.11.09 |

| [컴퓨터구조] I/O (0) | 2022.11.03 |

| [컴퓨터구조] External Memory(2) (0) | 2022.10.31 |

| [컴퓨터구조] External Memory(1) (0) | 2022.10.19 |